作者:泛林集团 Semiverse Solutions 部门半导体工艺与整合高级工程师王青鹏博士

持续的器件微缩导致特征尺寸变小,工艺步骤差异变大,工艺窗口也变得越来越窄[1]。半导体研发阶段的关键任务之一就是寻找工艺窗口较大的优秀集成方案。如果晶圆测试数据不足,评估不同集成方案的工艺窗口会变得困难。为克服这一不足,我们将举例说明如何借助虚拟制造评估 DRAM 电容器图形化工艺的工艺窗口。

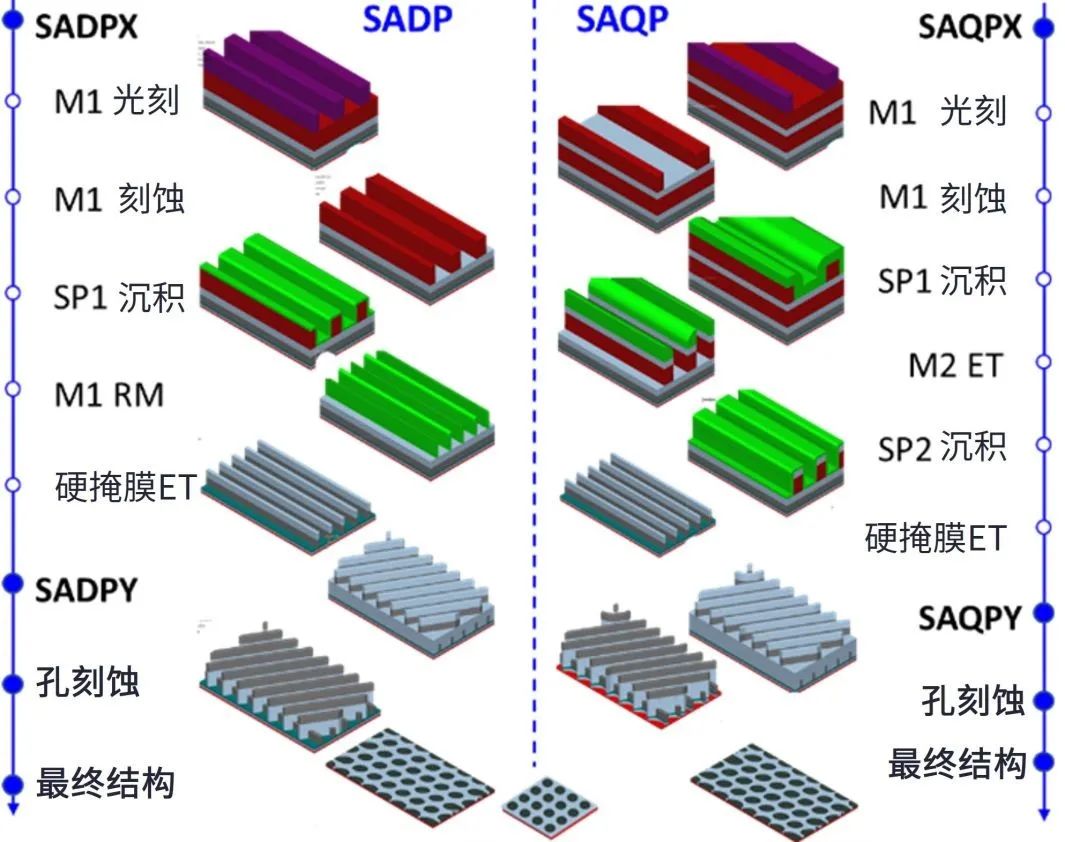

在 DRAM 器件开发中,必须在硅晶圆上刻蚀用于存储电荷的电容孔阵列。可用来制造 40nm 孔阵列的图形化方案包括极紫外光刻刻蚀、四重光刻刻蚀、双自对准双重图形化技术 (SADP)(80nm芯轴间距)和双自对准四重图形化技术 (SAQP)(160nm芯轴间距)。在这项研究中,我们选择了浸润式双 SADP 和 SAQP 图形化方案,并对其工艺灵敏性和工艺窗口进行了比较。我们为每个图形化方案 (SADP和SAQP) 建立了虚拟工艺流程(如图1),并将电容器孔面积作为电容及其均匀性分析的衡量标准。为了算出孔面积的变化范围,我们在 SEMulator3D 中使用结构搜索,寻找 4×4 孔阵列中电容器孔面积的最小值和最大值,并计算出平均面积和面积差值。图2显示了一次输出结构的测量结果,其中确定了结构中孔面积的最小值和最大值。

图1:SADP和SAQP的主要工艺步骤

图2:最小面积与最大面积的虚拟测量结果

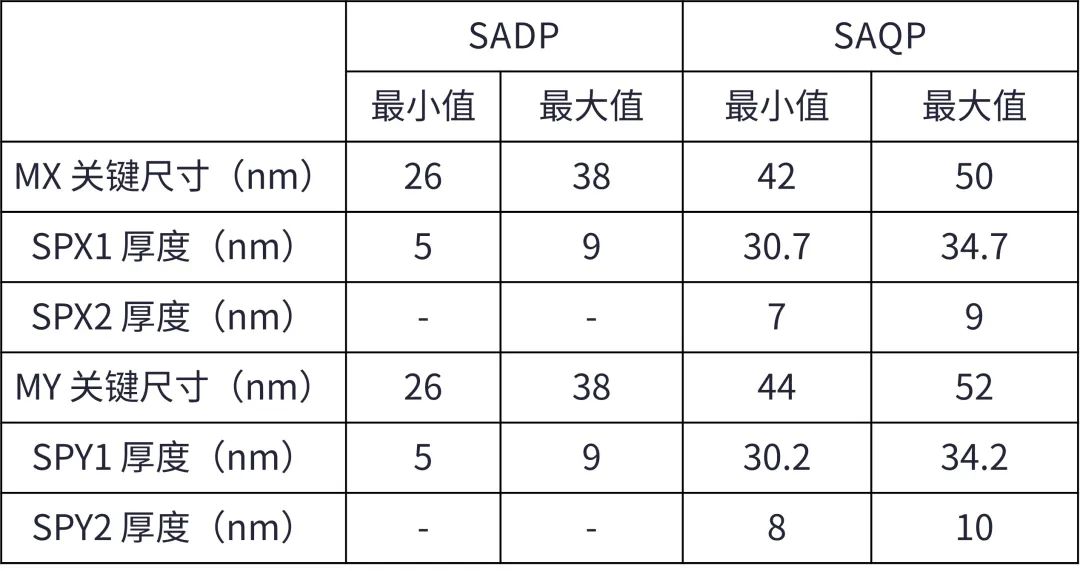

基于以上的虚拟流程和测量,我们使用 SEMulator3D 分析模块,进行了3000次蒙特卡罗实验。我们将芯轴关键尺寸和间隔层厚度设置为实验设计的输入参数,将平均面积和面积变化范围设置为输出参数。表1列出了 SADP 和 SAQP 工艺的输入参数值范围。虚拟实验设计结果帮助我们研究每项输入对平均面积和面积变化范围的影响。在表1中,MX 表示 X 方向芯轴关键尺寸;MY 表示 Y 方向芯轴关键尺寸;SPX1 表示 X 方向第一个间隔层厚度;SPX2 表示 X 方向第二个间隔层厚度;SPY1 表示 Y 方向第一个间隔层厚度;SPY2 表示 Y 方向第二个间隔层厚度。

表1:实验设计变量及输入范围

平均面积越大、面积变化范围越小,电容分布就越密集且均匀。通常认为,平均面积在900nm2至1100nm2之间,面积变化范围小于200nm2被定义为实验成功。在特定条件下,可以为工艺窗口算出成功模拟实验在总体实验所占比率(称为规格内比率),从而生成平均值和3-sigma(±3*标准差)分布。这个比率表示产生成功标准范围内平均面积和面积变化范围需要的输入组合比例。

为了最大化平均±3 sigma窗口中的实验成功次数,可以通过调整输入工艺参数平均值的方法,优化规格内比率[2]。如果优化后的规格内比率仍然不够高,还可以通过提高规格 (3 sigma) 要求,进一步对其进行优化。我们计算了不同条件下 SADP 和 SAQP 工艺的规格内比率。在 3 sigma 分布相同的情况下,SADP 工艺的规格内比率比 SAQP 工艺高约10%。调整芯轴关键尺寸的 3-sigma 规格后,SADP 工艺的规格内比率接近100%。当芯轴关键尺寸相同时,SAQP 工艺的规格内比率较低,表明 SAQP 工艺窗口需要进一步紧缩。

结论

在这项研究中,我们使用虚拟制造为先进 DRAM 结构中的电容器形成工艺进行了工艺窗口评估和优化。虚拟评估提供了明确且可量化的指导,帮助我们判断在先进 DRAM 结构中使用不同图形化方案的工艺难题。最重要的是,我们能在晶圆实验前确定每个图形化方案的最佳工艺目标组合和条件允许的最大工艺窗口。

参考资料:

1. A.J., Strojwas, 2006 IEEE International Symposium on Semiconductor Manufacturing (pp. xxiii-xxxii).

2. Q. Wang, Y. D. Chen, J. Huang, W. Liu and E. Joseph, 2020 China Semiconductor Technology International Conference (CSTIC) (pp. 1-3).