本文转载自:英飞凌工业半导体微信公众号

作者简介:

文:Paul Sochor, Andreas Huerner, Qing Sun, Rudolf Elpelt

德国英飞凌科技股份公司

通讯作者:Paul Sochor,paul.sochor@infineon.com

摘 要

本文探讨了影响高速SiC MOSFET开关特性的关键因素,包括器件特性、工作条件和外部电路;解释了开关损耗的主要影响因素,并确定了影响器件行为和使用的重要因素,这些因素可以显著提升SiC MOSFET在功率电路中的开关性能。

1. 引言

碳化硅(SiC)MOSFET支持功率电子电路以超快的开关速度和远超100V/ns和10A/ns的电压和电流摆率下工作。SiC MOSFET还具有非常出色的导通特性和高温特性。与传统的硅基功率半导体相比,SiC MOSFET具有非常低的器件工作损耗,可以实现高度紧凑且高效的功率转换器解决方案[1]。

SiC MOSFET的开关性能不仅取决于器件本身的特性,在很大程度上还取决于器件的外部电路和工作条件。

SiC MOSFET的开关行为是十分复杂的话题。数据手册中所提供的数值,往往只能表示器件在非常具体的测试环境中、在若干特定条件下的性能。而在实际的电源电路条件下,器件的真实性能取决于很多因素。

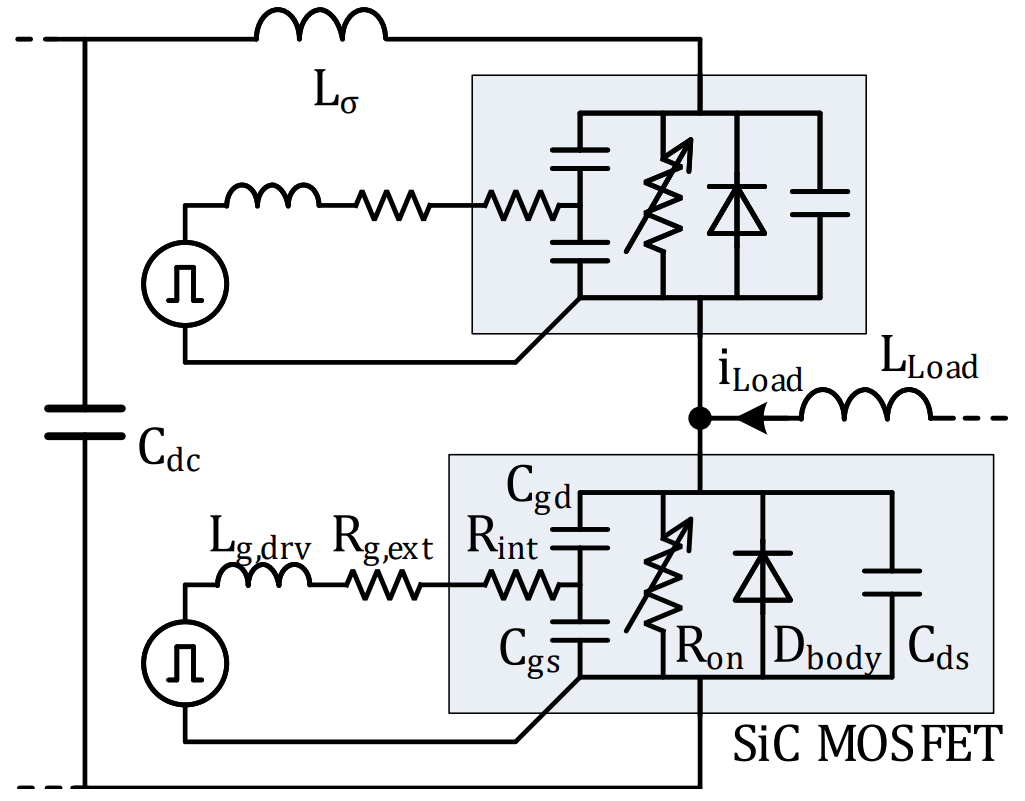

图1:SiC MOSFET半桥电路简图。

优化电源电路的设计和工作条件,可以显著提高SiC MOSFET的开关性能。

本文将使用实测数据,重点介绍SiC MOSFET开关行为的许多重要方面。本文将重点讨论,在标准的半桥电路等硬开关工作条件下的快速开关分立式CoolSiC™ MOSFET(见图1)。

2. 开关行为和损耗

开关损耗和导通损耗是导致功率转换器半导体器件焦耳热的两大因素。尽管SiC MOSFET的导通损耗主要取决于器件本身的特性和工作条件(例如,栅极电压、负载电流和器件温度),但开关损耗有着更加明显也更加复杂的特性。

影响器件总开关损耗主要有三个因素:开通能量EON、关断能量Eoff和反向恢复能量Erec。其占比通常取决于器件的特性、操作条件和外部电路。除此之外,在开关过程中,还可能会出现其它的损耗,例如由寄生导通引起的损耗[2]。

影响开关损耗的器件特性包括芯片技术、芯片尺寸、封装类型和内部栅极电阻(Rint)。对开关损耗影响最大的工作条件为:芯片结温、直流母线电压、栅极电压和负载电流。我们将首先探讨它们之间的关系及其对开关行为的影响,然后,在下一节探讨封装和外部电路的影响。

2.1. MOSFET关断

在关断过程中,MOSFET输出电容被充电,于是阻断了整个直流母线电压,随后,续流器件的体二极管接管负载电流。MOSFET的关断特性对温度的依赖性非常微弱,但由于半导体具有非线性C-V特性,因此,其关断特性对工作电压依赖性比较明显。

在开关速度和负载电流方面,有一些重要的方面需要考虑。在中低电流时,关断特性主要受负载电流影响,栅极电阻的影响不大。这是因为在米勒阶段,当器件的输出电容Coss被低恒定电流充电时,较低的Rg,ext并不能加快充电速度。这就解释了为何在低Rg,ext值时,低电流的开关瞬态相对较慢。

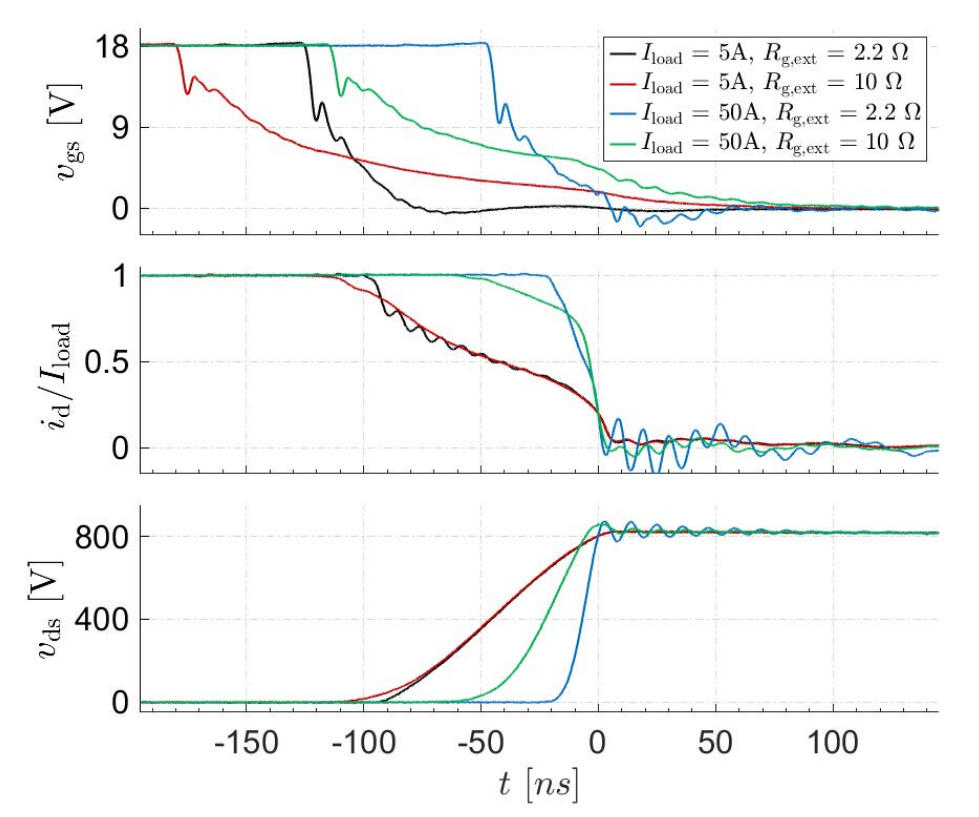

图2:T=25°C时,不同电流和栅极电阻的关断波形对比。

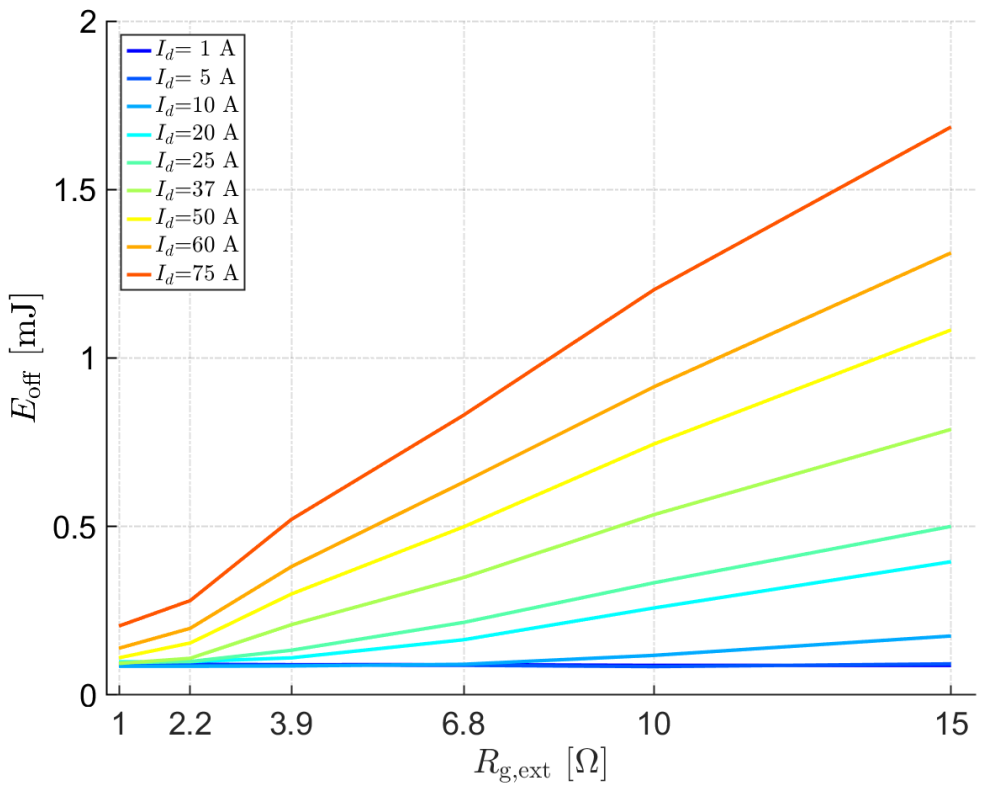

图3:T=25°C时,在不同电流和栅极电阻下,测得的关断能量的对比。

图2和图3突出显示了这种效应,图中显示了一个采用TO247-4封装的1200V、20mΩ CoolSiC™ SiC MOSFET的关断行为。在图2中,vds和id的开关波形在5A负载电流下几乎相同(虽然栅极电阻存在差异);但在50A的高电流下,情况就不一样了。

图3显示了,在低电流下,关断能量Eoff在很大的栅极电阻范围内保持恒定。其最小能量取决于为输出电容充电所需的能量Eoss。它可能是硬开关电路中最低的Eoff。Eoff的Eoss部分存储在Coss中,并在器件再次导通时,以热量的形式耗散。虽然,严格意义上来讲,这种耗散是在导通时发生的,但它被视为关断损耗。在较高的电流和/或较慢的开关中,来自换流过程的额外能量贡献也被包含在Eoff中(不含Eoss)。这些是在实际的关断过程中耗散的。

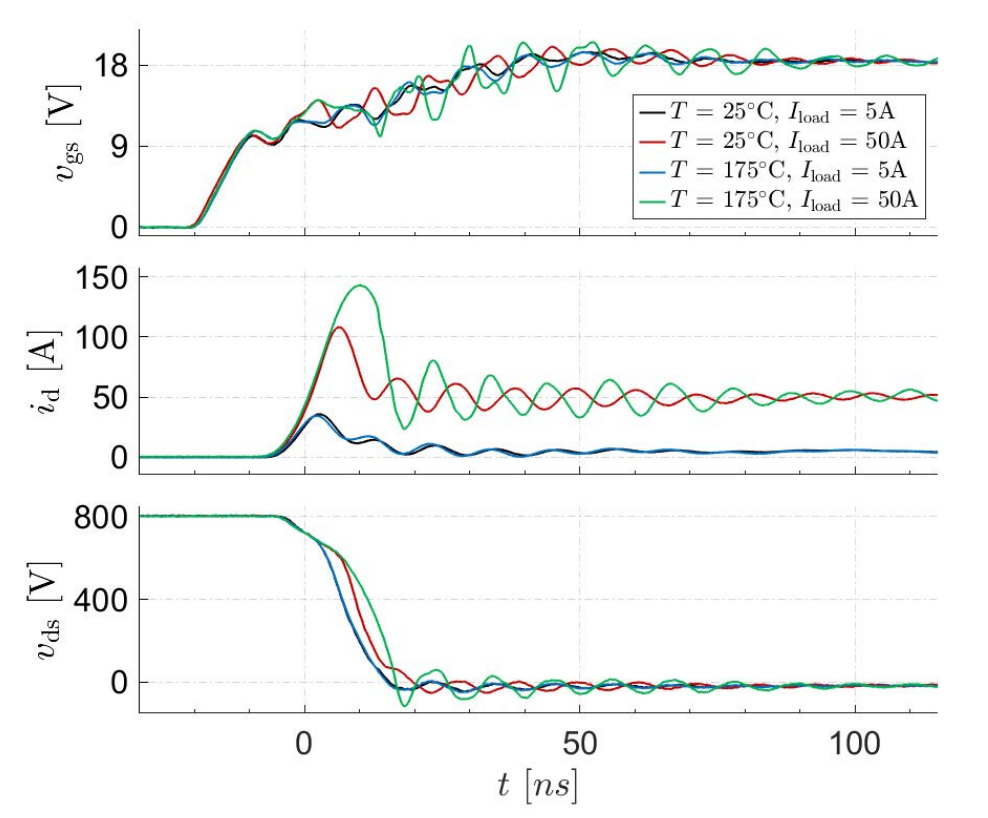

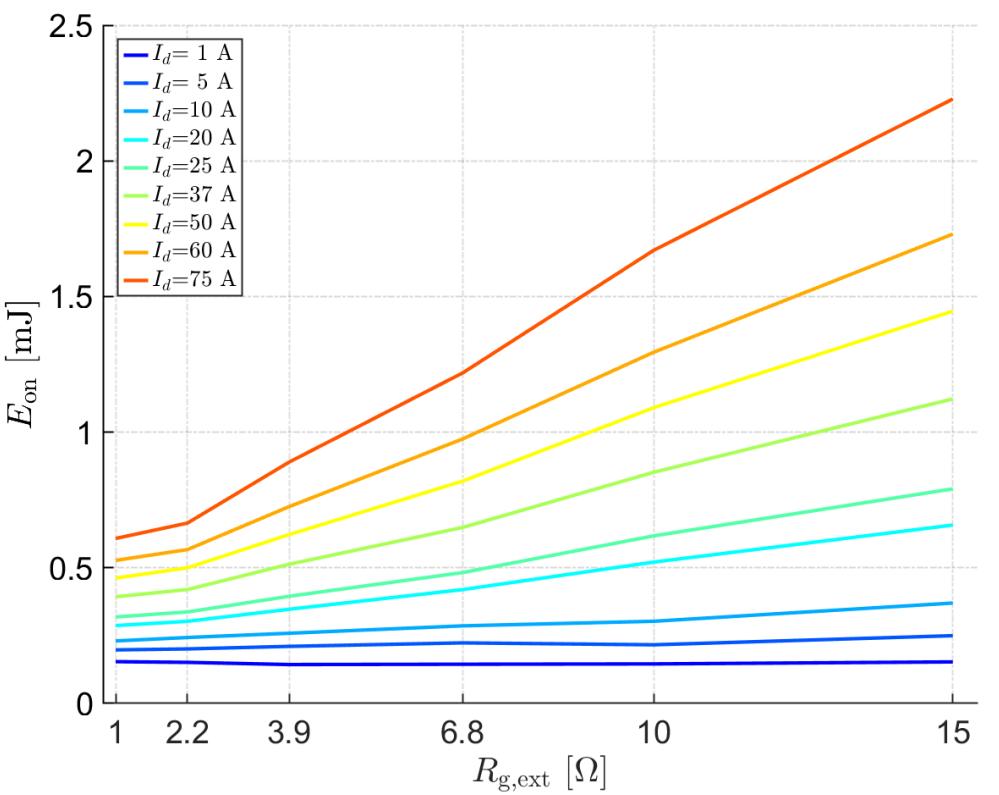

图4:不同电流和温度下的导通波形对比(均为Rg,ext =2.2Ω)。

图5:T=25°C时,在不同电流和栅极电阻下,测得的导通能量的对比。

2.2. 体二极管关断

体二极管的关断过程,也称反向恢复,是SiC MOSFET开关行为的一个重要组成部分。

二极管反向恢复,描述了从器件的漂移区去除存储的双极等离子体电荷的过程。SiC MOSFET的体二极管具有独一无二的特性,这使得它的反向恢复行为与IGBT电路中的硅二极管大不相同。SiC MOSFET体二极管中存储的双极电荷,显示出对温度和电流的明显依赖。

在低电流或低温下,双极电荷非常小。从开关的角度来看,体二极管在这些条件下的行为,与单极肖特基二极管相似。

然而,随着温度的上升和电流的增加,体二极管存储的双极电荷越来越多,并表现出更多的双极开关特性。

体二极管的反向恢复会产生开关损耗,从而导致半导体器件中产生焦耳热。这需要在计算器件的整体损耗时,加以考虑。除此之外,二极管反向恢复会严重影响MOSFET的导通转换,包括MOSFET导通损耗(见3.2)。

2.3. MOSFET开通

开通瞬态过程不仅取决于主动导通的MOSFET的器件特性,而且还在很大程度上,取决于其被动续流器件。瞬态波形和开关能量各不相同,具体取决于续流器件是肖特基二极管还是其他SiC MOSFET。如果是MOSFET,续流器件输出电容的充电过程及其体二极管反向恢复发挥着重要作用。

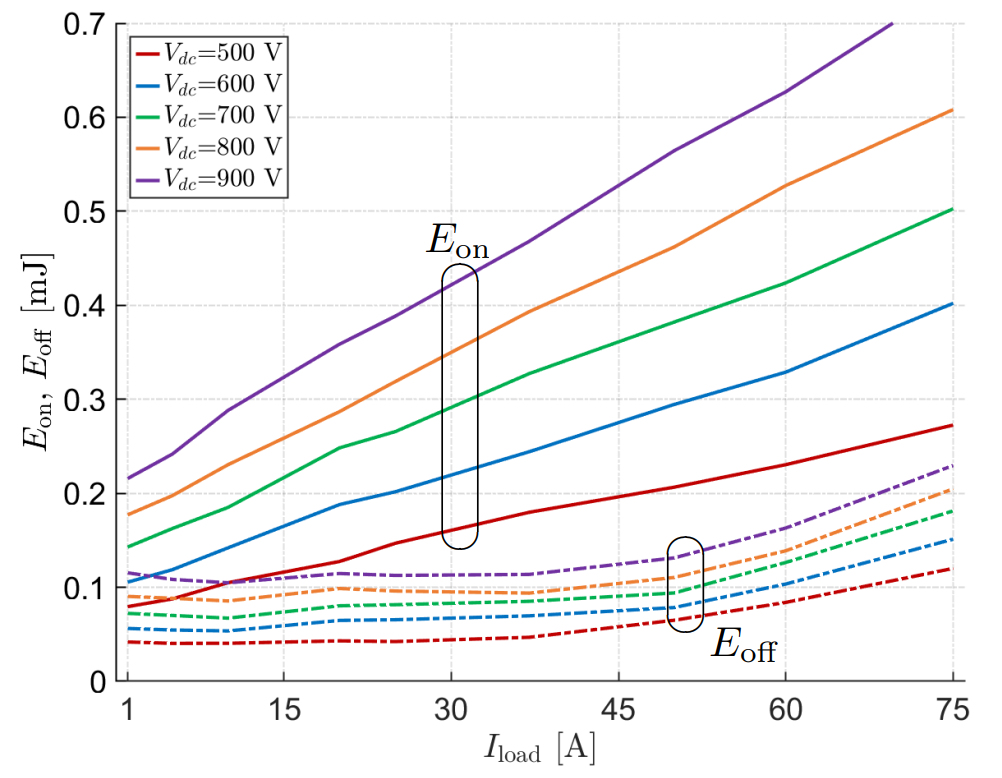

在关断期间,Coss由恒定的负载电流充电;在开通期间,Coss由恒定的电压源(即直流链路电容器)充电。当MOSFET快速开关时,哪怕是非常小的负载电流,上述这种差异也会导致典型的反向电流浪涌(见图4)。开通过程的速度完全由有源开关MOSFET控制。由于开关速度受电流、电压、温度和栅极电阻的影响,因此,开通能量对这些参数表现出了明显的依赖性(见图5和图6)。

与关断期间不同,开通期间的开关能量受温度影响很大。虽然MOSFET的I-V特性确实有一定的温度依赖性,会影响开关能量,但总体影响很小。对开通温度依赖性的主要贡献,要数体二极管的反向恢复,以及在开通期间,存储在二极管中的双极电荷量。

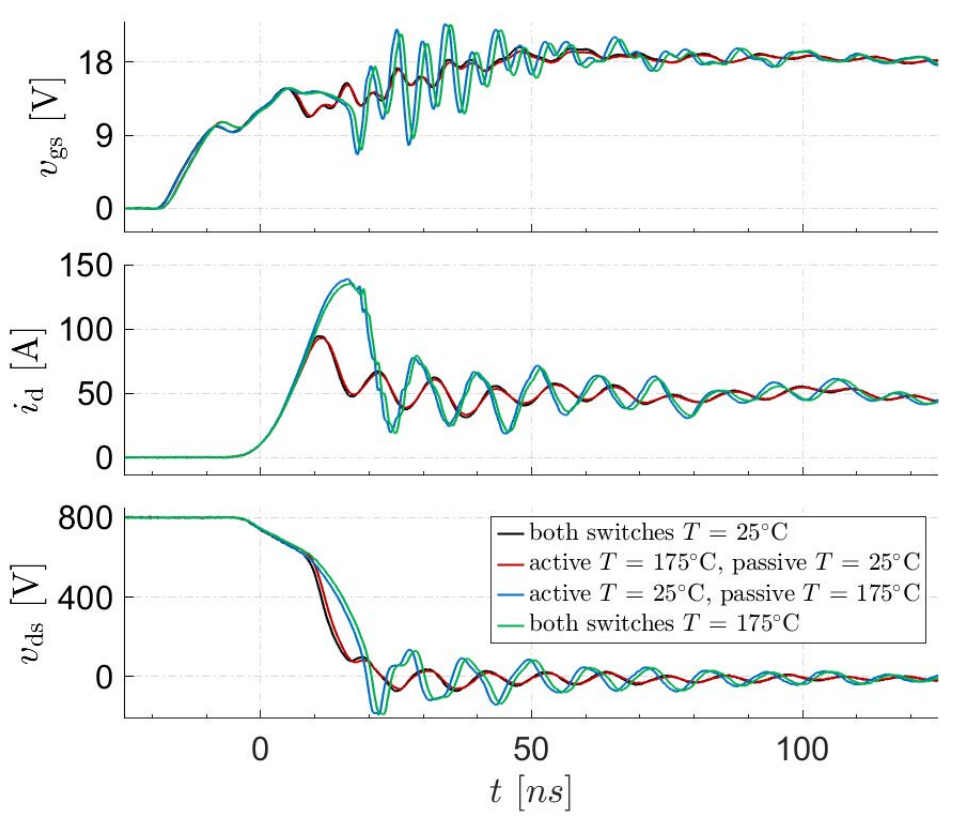

图7突出显示了,温度对有源开关SiC MOSFET导通行为的影响。在实验中,将主动和被动(低边和高边)器件安装在不同的加热板上,分别控制其温度。图7表明,无源器件(体二极管)的温度对有源开关的开关行为有很大影响,而有源开关的温度影响很小。原因在于反向恢复期间的电荷流动,这会影响体二极管和有源开关MOSFET。

电路设计人员可以通过调整驱动电压,来减轻双极电荷的影响,并降低开关损耗[3]。另外,缩短死区时间也能提升性能(见3.2)。

图6:在不同的直流母线电压下,T=25°C时,快速导通和关断能量的对比。

图7:在不同温度下,有源和无源开关的快速导通。

3. 外部电路的影响

在快速开关应用中,外部电路对器件的性能有着巨大的影响。许多论文都讨论了功率半导体的外部影响[4]-[6],却往往低估了外部电路对快速开关SiC MOSFET性能的影响。其主要影响包括但不限于,外部栅极电阻(Rg,ext)、换向回路杂散电感Lσ、栅极阻抗、栅极驱动器摆率和死区时间[3]、[7]。

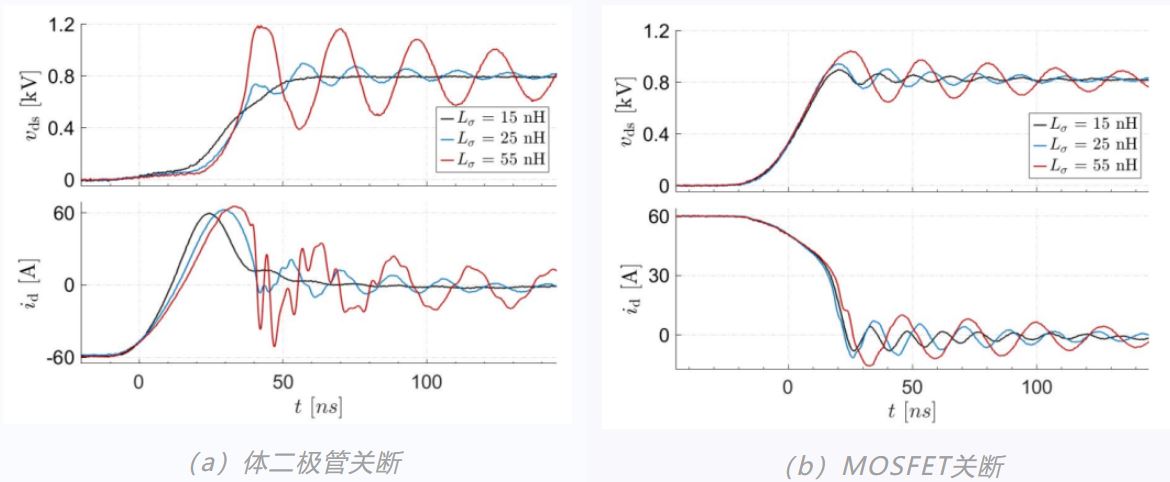

3.1. 换流回路杂散电感

通过降低Rg,ext来加快开关速度,可以降低开关损耗。但在实践中,Rg,ext的最低值是受限的。对于半导体,此下限由其器件的最大额定值规定。与电路中的寄生杂散电感一起,快速瞬变会导致高过冲电压超过器件的允许额定值。因此,应当将Rg,ext设定在这些额定值的范围内[8]。

在电源电路中的寄生元素中,换向回路杂散电感Lσ对器件的电压过冲的影响,可以说是最大的。这种杂散电感包括,主换流回路内所有部分电感(封装和外部电路)。

对于SiC MOSFET,在最大工作温度和电流下,体二极管关断期间,器件电压通常是设计电源电路的最关键的条件。在此期间,大量的双极电荷存储在体二极管中,关断时产生反向恢复电流。制约电流变化的大杂散电感,会导致体二极管的dv/dt很高,以及导致电场迅速扫除漂移区中的自由载流子。如果在器件电流自然降低到零之前,发生这种情况,那么,剩余的器件电流可能会在高di/dt下瞬变,并导致器件出现不希望的过冲电压。

如图8a所示,当SiC MOSFET在具有高杂散电感的电源电路中,以非常快的开关速度运行时,可能会发生这种跳变(snap-off)效应。除了高损耗和过冲电压外,高杂散电感还会导致系统中其他元件的电磁干扰问题。MOSFET关断时的过冲电压,通常并不那么重要(对比图8b)。

因此,精心设计的低电感电源电路是实现干净、快速开关瞬态和低开关能量的关键。

图8:T=150°C时,不同换向回路杂散电感Lσ的快速关断行为比较。

3.2. 死区时间

在图1所示的典型半桥或全桥配置中,SiC MOSFET的体二极管仅在死区时间内传导电流。体二极管只能在死区时间内,在其漂移区建立双极等离子体。该建立过程需要一定的时间,来建立稳态等离子体条件。这可能需要几百纳秒,甚至更长的时间,具体取决于器件的技术和电压等级。如果死区时间较短(小于在漂移区内产生稳态等离子体浓度所需的时间),则二极管关断时,必须去除的电荷较少[3]、[7]。

在需要体二极管换向的应用(即桥式拓扑)中,缩短死区时间,是提升SiC MOSFET性能的有效方式。由于体二极管的双极电荷会增加有源开关和无源开关的损耗(Eon和Erec),因此,缩短死区时间,从而减少双极电荷,也可以减少这两类开关损耗。如第2.3节所述,Eon显著的温度依赖性主要是因为体二极管的双极电荷。如果将死区时间设置为足够短的间隔,那么,就可以尽早停止等离子体的产生,从而有效地消除对开关行为的影响。

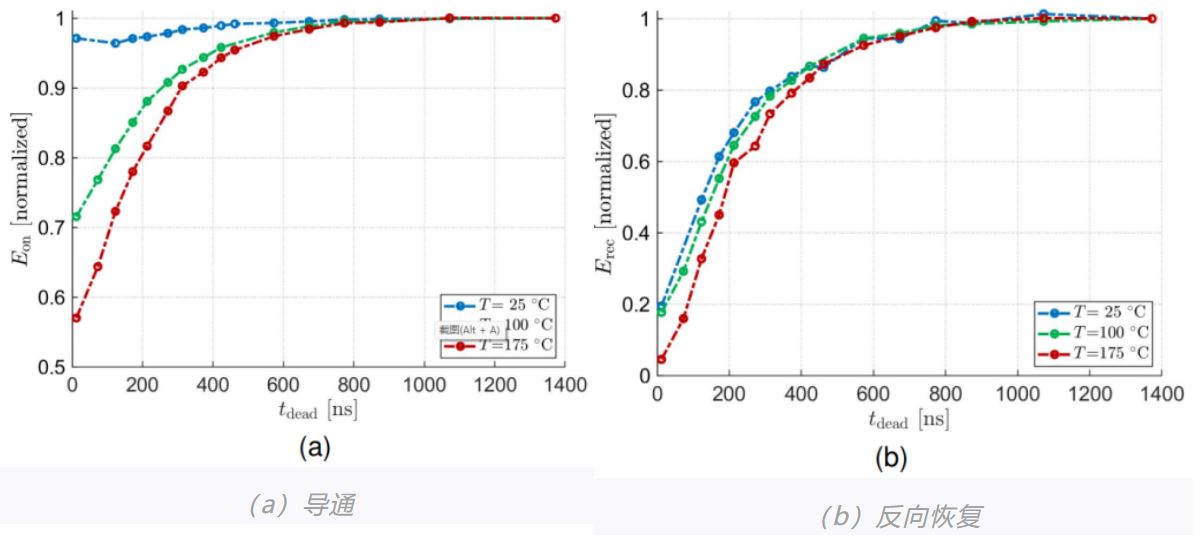

图9:iLoad=50A时,死区时间的缩短对开关能量的影响。

图10:死区时间和温度对导通波形的影响。

图9显示了死区时间、导通能量和反向恢复能量之间的关系。在本测量中,实际的死区时间是通过测量两个栅极电压而确定的。

从图9可以看到,在高温时,短死区时间对开关能量的影响特别有效;在低温下,等离子体密度较低时,死区时间的影响有限。如果死区时间设置得太短,由于两个开关的同时导通时间非常短,开关能量可能会再次增加。因此,必须根据栅极驱动器和控制器的特性,适当调整死区时间。

由图10可见,在175°C时,MOSFET导通波形几乎等于25°C时的波形,这是因为死区时间较短时,缺乏双极等离子体。在这种特殊的情况下,SiC MOSFET的体二极管的行为与肖特基二极管类似。低等离子体密度对其开关行为几乎没有影响。

4. 封装的影响

器件封装对SiC MOSFET的开关性能有很大影响。与较大的模块相比,小型分立式封装通常具有低杂散电感和低Lσ*Inom的特点,适用于在高开关频率下工作的电路。由于尺寸紧凑,它们还为电路设计人员带来了更大的灵活性。然而,在以高速电路为目标时,设计人员必须将某些封装特性牢记于心。

4.1. 4引脚与3引脚

传统上,单开关分立式功率半导体具有漏极、栅极和源极三个电气连接引脚。随着快速开关器件的出现,具有4个引脚的器件(其中一个为驱动器提供额外的连接,即所谓的开尔文源)变得越来越普遍。尽管在物理上相似,但实际上,3引脚和4引脚封装的SiC MOSFET在开关性能方面,有着显著的差异。第4个引脚的真正优势,特别是在快速开关应用中的优势,往往被低估了。

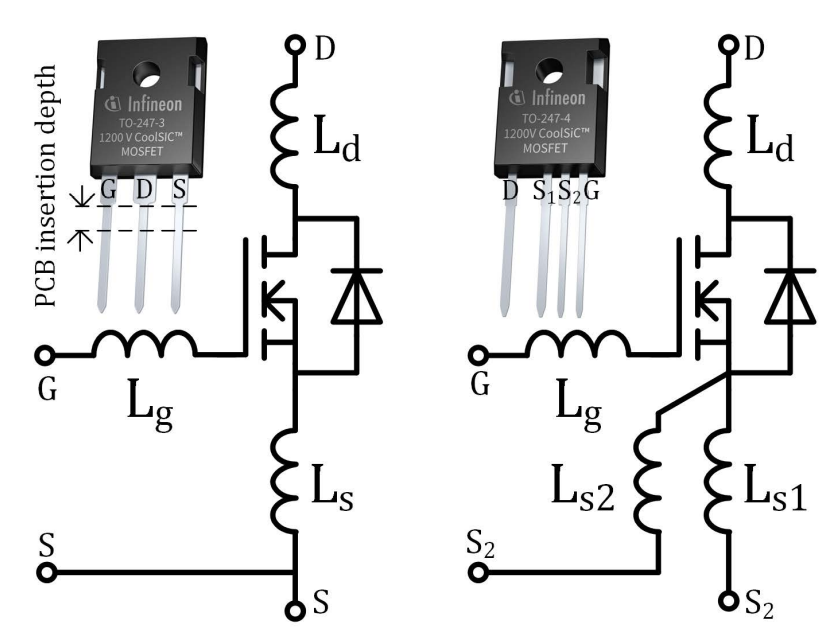

图11:4引脚和3引脚型号的TO247封装

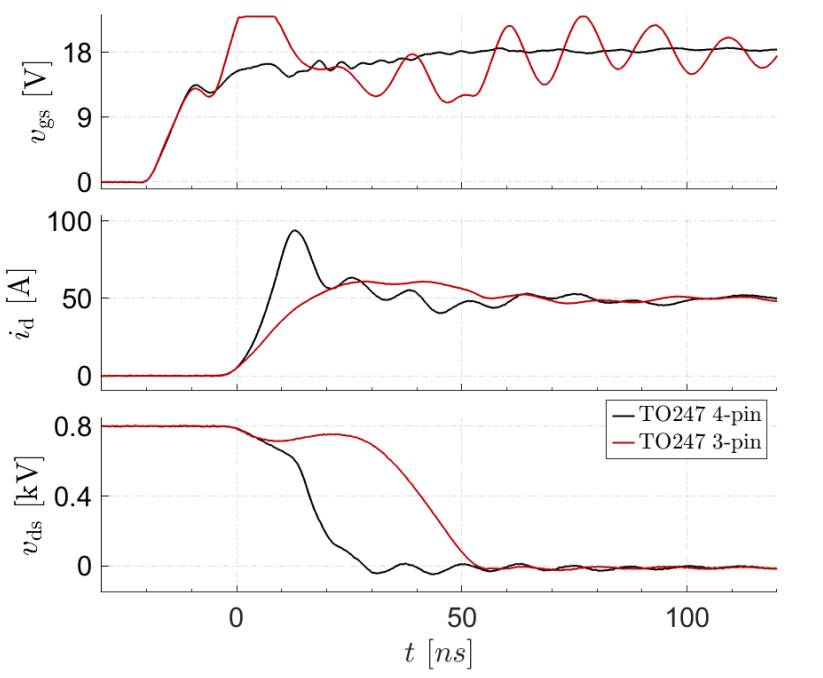

图12:T=25°C和50A时,4引脚和3引脚TO247封装在快速导通时的对比

图11对比了3引脚TO247封装和4引脚TO247封装的示意图。其中,3引脚TO247封装是标准的通孔封装,适用于功率半导体,具有悠久的历史,在行业中广为使用。它有一个源极引脚,由负载电路和栅极驱动电路共用。该引脚为MOSFET提供公共源极电感Ls,用作负载电路和栅极电路之间的反馈回路。

传统的标准化3引脚TO247封装因其引脚长度和引脚结构(栅极-漏极-源极)(其中,栅极和源极引脚之间的距离最远)直接导致反馈电感相对较大。引脚是基于过去的经验进行配置的,遗憾的是,这导致栅极和源极引脚之间产生了一个高电感回路。它还导致3引脚器件在引脚插入印刷电路板(PCB)的深度方面,非常敏感。器件封装和PCB之间的距离稍有增加,就会明显增加反馈电感。

另一方面,4引脚TO247封装有两个带有独立键合线的源极引脚,一个用于栅极驱动电路,另一个用于负载电路。它还提供了更有利的引脚配置,电感环路的面积更小:漏极-源极-源极-栅极。因此,4引脚TO247封装在负载和栅极电路之间几乎没有反馈。

3引脚TO247封装的栅极反馈与频率有关,因此,它对开关的影响程度,取决于实际的开关速度。当使用较大的Rg,ext慢速开关,或者当功率半导体的开关速度本来就很慢时,栅极反馈的影响可能不明显。但对于SiC MOSFET的快速开关瞬态而言,这种影响非常明显。Ls中的感应电压抵消了栅极驱动电压,从而有效地减缓了开关过程,并增加了开关损耗。

图12在相同的设置和开关条件下,比较了相同芯片的4引脚TO247和3引脚TO247 SiC MOSFET封装,强调了栅极反馈的影响。由图可知,即使在非常低的Rg,ext下,3引脚封装的强大栅极反馈也会防止快速开关。在较高电流时,其反馈电感的影响通常比在较低电流时更强。

值得注意的是,当Lσ过高时,vds中高过冲电压会限制4引脚器件的开关速度,而3引脚器件可能不会出现这种情况。后者不能、也不适合非常快速的开关。不过,它们适用于不需要快速开关的应用。

5. 总结与结论

快速SiC MOSFET的开关行为是设计高效的功率转换器电路的一个重要因素。虽然导通损耗(由器件特性和工作条件决定)几乎没有提升性能的潜力,但实际上,可以通过优化电路,来降低开关损耗。考虑到工作条件和外部电路对开关行为的影响,电路设计人员有很大的空间,来改进性能。

本文探讨了电流、电压、温度和栅极电阻对开关损耗Eon、Eoff和Erec的各种依赖性,以及外部电路的影响。对于快速开关SiC MOSFET,在高温和大电流下,体二极管关断期间的电压过冲,通常是提高开关速度的限制因素。经过优化的低电感电路设计,可实现更快的开关和更低的损耗。

死区时间对SiC MOSFET的开关行为有明显的影响。较短的死区时间减少了反向恢复期间必须去除的双极电荷,从而减少了导通损耗和恢复损耗。此外,它还降低了二极管关断时的电压过冲,为更快速的开关,提供了更大的空间。在非常短的死区时间td<100ns下,开关行为和损耗几乎与温度无关。

器件封装会对开关性能产生重大影响。分立式3引脚封装没有单独的引脚来连接栅极驱动器,由于其共源电感较大,表现出了非常强的栅极反馈。这种栅极反馈导致其不适用于快速开关应用。3引脚器件的开关损耗明显高于4引脚器件。3引脚器件的开关性能受到器件封装的限制,4引脚器件则受到外部电路或芯片本身特性的限制。面对快速开关应用,采用具备两个独立源极引脚的封装的SiC MOSFET器件是首选。

参考文献

[1] X. She, A. Q. Huang, O. Lucia, and B. Ozpineci, “Review of silicon carbide power devices and their applications,” IEEE Trans. Ind. Electron., vol. 64, no. 10, pp. 8193–8205, 2017.

[2] K. Sobe, T. Basler, and B. Klobucar, “Characterization of the parasitic turn-on behavior of discrete CoolSiC™ MOSFETs,” in PCIM Europe, 2019.

[3] P. Sochor, A. Huerner, M. Hell, and R. Elpelt, “Understanding the turn-off behavior of SiC MOSFET body diodes in fast switching applications,” in PCIM Europe, 2021.

[4] Z. Chen, D. Boroyevich, and R. Burgos, “Experimental parametric study of the parasitic inductance influence on MOSFET switching characteristics,” in ECCE ASIA, 2010.

[5] J. Wang, H. S.-h. Chung, and R. T.-h. Li, “Characterization and experimental assessment of the effects of parasitic elements on the MOSFET switching performance,” IEEE Trans. Power Electron., vol. 28, no. 1, pp. 573–590, 2013.

[6] K. Wada and M. Ando, “Switching loss analysis of SiC-MOSFET based on stray inductance scaling,” in IEEE IPEC-Niigata 2018 – ECCE Asia, 2018, pp. 1919–1924.

[7] R. Horff, A. Maerz, and M. Bakran, “Analysis of reverse-recovery behaviour of SiC MOSFET body-diode - regarding dead-time,” in PCIM Europe, 2015.

[8] P. Sochor, A. Huerner, and R. Elpelt, “Commutation loop design for optimized switching behavior of CoolSiC™ MOSFETs using compact models,” in PCIM Europe, 2020.